ASPLOS 2023 Tutorial

Real-world Processing-in-Memory Systems for Modern Workloads

# Hands-on Lab

Programming and Understanding a Real Processing-in-Memory Architecture

### Dr. Juan Gómez Luna Professor Onur Mutlu

Sunday, March 26, 2023

### **Real PIM Tutorial: Hands-on Lab**

ASPLOS 2023 TUTORIAL: REAL-WORLD PROCESSING-IN-MEMORY SYSTEMS FOR MODERN WORKLOADS. MARCH 26, 2023

1/7

#### Programming and Understanding a Real Processing-in-Memory Architecture

Instructors: Dr. Juan Gómez Luna, Prof. Onur Mutlu

#### 1. Introduction

In this lab, you will work hands-on with a real processing-in-memory (PIM) architecture. You will program the UPMEM PIM architecture [1] [2] [3] [4] for several workloads and will experiment with them. Your main goals are (1) to become familiar with the UPMEM PIM system organization (as an example of real-world memory-centric computing system), (2) to understand the UPMEM programming model and write your own code, and (3) to understand the microarchitecture and instruction set architecture (ISA) of UPMEM's PIM core (called DRAM Processing Unit, DPU).

As we introduced in this tutorial, the UPMEM PIM architecture is composed of multiple DPUs (up to 2,560), each of which has access to its own DRAM bank (called *Main RAM, MRAM*) and its own scratchpad memory (called *Working RAM, WRAM*). You can find a full description of the UPMEM PIM system in [3, 4].

#### 2. Your Task 0/4: Accessing the UPMEM PIM Server

UPMEM has granted us with remote access to servers with UPMEM DIMMs in a datacenter.

Our username is: ethasplos23 and we are part of the group upmem0063 (ETH ASPLOS 2023 team). You can download the SSH private key used to connect the machines from here: https://events.safari.ethz.ch/asplos-pim-tutorial/lib/exe/fetch.php?media=upmemcloud.ethasplos23.zip (download and un-zip!)

Put the following base configuration in your .ssh/config file:

Host upmemcloud\* User ethasplos23 Hostname %h.cloud.upmem.com IdentityFile ~/.ssh/upmemcloud\_ethasplos23 StrictHostKeyChecking no UserKnownHostsFile=/dev/null

You can connect to the booked machine anytime until 6am (Vancouver time) on Monday, March 27, 2023.

The booked machine for this period is upmemcloud5 with '20 UPMEM-P21'. You can connect to it by doing: ssh upmemcloud5, if you have the private SSH key and the .ssh/config file provided above.

The machine is installed with the latest and greatest UPMEM SDK version (also available on https://sdk. upmem.com). As an introduction, the public demonstration program doing a trivial checksum in parallel on one DPU can be run by doing: git clone https://github.com/upmem/dpu\_demo.git

cd /dpu\_demo/checksum

NR\_DPUS=1 make test

Please read the entire Section 2 before you access the server.

In summary, the steps are:

1. Paste the configuration into .ssh/config.

- 2. Copy the private key upmemcloud\_ethasplos23 to your .ssh folder. You may need to change permissions, as indicated in Section [2.1]

- ssh upmemcloud5 from the terminal. Note that the server is already reserved for us. No booking is needed.

### SAFARI

## How to Access the UPMEM PIM Server?

- Paste the configuration into .ssh/config Host upmemcloud\* User ethasplos23 Hostname %h.cloud.upmem.com IdentityFile ~/.ssh/upmemcloud\_ethasplos23 StrictHostKeyChecking no UserKnownHostsFile=/dev/null

- 2. Copy the private key upmemcloud\_ethasplos23 to your .ssh folder. You may need to change permissions

3. ssh upmemcloud5 from the terminal

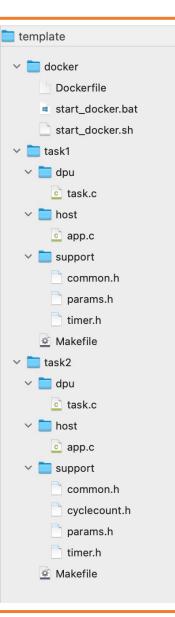

# **Template Files**

- Contain templates for task 1 and task 2

- Task 2's template can be used for the remaining tasks

### SAFARI

## Task 1: CPU-DPU and DPU-CPU Transfers

### • Use serial, parallel, and broadcast transfers

Your tasks are as follows:

- Write a host program that exercises all types of data transfers between the host main memory and one or multiple MRAM banks. Concretely, there are three types of data transfers [2]: (1) serial, (2) parallel, and (3) broadcast. Serial and parallel transfers move data from main memory to the MRAM banks or vice versa. Broadcast transfers can only happen from the main memory to the MRAM banks.

- 2. Evaluate all different types of data transfers for data transfers of size (1) 1MB, (2) 24MB, (3) 48MB per DPU. Use different numbers of DPUs between 1 and 64.

| Serial Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Parallel Transfers                                                                                                                                                                                                                                                                                                           | Broadcast Transfers                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li><u>dpu_copy_to();</u></li> <li><u>dpu_copy_from();</u></li> <li>We transfer (part of) a buffer to/from each DPU in the <u>dpu_set</u></li> <li>DPU_MRAM_HEAP_POINTER_NAME: Start of the MRAM range that can be freely accessed by applications <ul> <li>We do not allocate MRAM explicitly</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>We push different buffers to/from a DPU set in one transfer <ul> <li>All buffers need to be of the same size</li> </ul> </li> <li>First, prepare (dpu_prepare_xfer); <ul> <li>then, push (dpu_push_xfer)</li> </ul> </li> <li>Direction: <ul> <li>DPU_XFER_TO_DPU</li> <li>DFU_XFER_FROM_DPU</li> </ul> </li> </ul> | <ul> <li>dpu_broadcast_to();</li> <li>Only CPU to DPU</li> <li>We transfer the same buffer to all DPUs in the dpu_set</li> <li>PMLASSET(opu_broadcast_toldpu_set, OPU_MEM_MEMP_POINTER_MEMP, 0, @stfers}_input_size_dov + sizes(1); OPU_MEM_MEMPLATER_TOTAL TO TRANSFER Size</li> </ul> |

| SAFARI Start | Sec. SECTOR J. Sec. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.                                                                                                                                                                                                                                                                   | SAFARI 75                                                                                                                                                                                                                                                                               |

### SAFAR

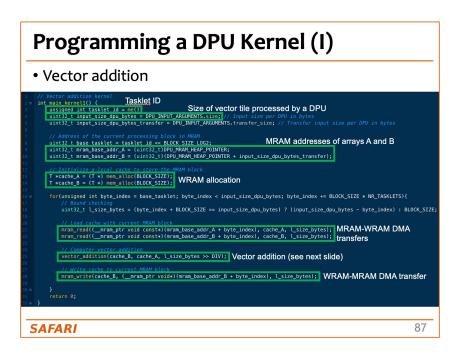

## Task 2: AXPY

Your tasks are as follows:

- 1. Write a DPU kernel that executes the AXPY operation  $(y = y + alpha \times x)$  [5] on every element of a vector. You have to (1) transfer two input vectors, Y and X, to the MRAM bank/s, (2) perform the AXPY operation with a variable number of tasklets, (3) write the results to the output vector, Y, and (4) transfer the output vector back to the host main memory.

- VA is a good reference code for this task

## Task 3: Operations and Datatypes

Your tasks are as follows:

- 1. Modify your AXPY DPU kernel to make it a vector addition (y = y + x) and to support other operations besides addition (i.e., subtraction, multiplication, division).

- 2. Evaluate the performance of your new kernel for different operations (addition, subtraction, multiplication, division) and data types (char, short, int, long long int, float, double).

• You will observe significant variations in arithmetic throughput for different operations and datatypes

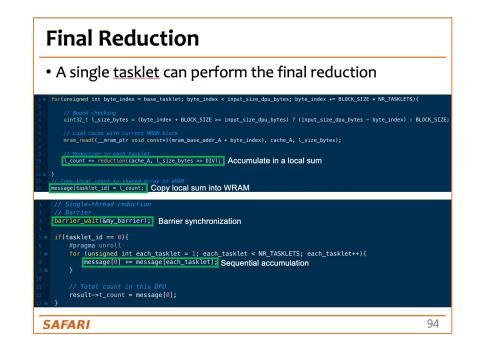

### **Task 4: Vector Reduction**

Your tasks are as follows:

- 1. Your vector reduction DPU kernel should have four different versions: (1) final reduction with a single tasklet, (2) final tree-based reduction with barriers, (3) final tree-based reduction with handshakes, (4) final reduction with mutexes.

- Performance differences due to the final reduction step

ASPLOS 2023 Tutorial

Real-world Processing-in-Memory Systems for Modern Workloads

# Hands-on Lab

Programming and Understanding a Real Processing-in-Memory Architecture

### Dr. Juan Gómez Luna Professor Onur Mutlu

Sunday, March 26, 2023