Table of Contents

Real-world Processing-in-Memory Architectures

Tutorial Description

Processing-in-Memory (PIM) is a computing paradigm that aims at overcoming the data movement bottleneck (i.e., the waste of execution cycles and energy resulting from the back-and-forth data movement between memory units and compute units) by making memory compute-capable.

Explored over several decades since the 1960s, PIM systems are becoming a reality with the advent of the first commercial products and prototypes.

A number of startups (e.g., UPMEM, Neuroblade) are already commercializing real PIM hardware, each with its own design approach and target applications. Several major vendors (e.g., Samsung, SK Hynix, Alibaba) have presented real PIM chip prototypes in the last two years.

Most of these architectures have in common that they place compute units near the memory arrays. But, there is more to come: Academia and Industry are actively exploring other types of PIM by, e.g., exploiting the analog operation of DRAM, SRAM, flash memory and emerging non-volatile memories.

PIM can provide large improvements in both performance and energy consumption, thereby enabling a commercially viable way of dealing with huge amounts of data that is bottlenecking our computing systems. Yet, it is critical to examine and research adoption issues of PIM using especially learnings from real PIM systems that are available today.

This tutorial focuses on the latest advances in PIM technology. We will (1) provide an introduction to PIM and taxonomy of PIM systems, (2) give an overview and a rigorous analysis of existing real-world PIM hardware, (3) conduct hand-on labs using real PIM systems, and (4) shed light on how to enable the adoption of PIM in future computing systems.

Livestream

Organizers

Agenda (February 26, 2023)

- 8:00am-8:40am, Prof. Onur Mutlu, “Memory-centric computing: Introduction to PIM as a paradigm to overcome the data movement bottleneck”.

- PIM taxonomy: PNM (processing near memory) and PUM (processing using memory).

- 8:40am-10:00am, Dr. Juan Gómez Luna, “Processing-Near-Memory: Real PNM Architectures Programming General-purpose PIM”.

- PNM prototypes: Samsung HBM-PIM, SK Hynix AiM, Samsung AxDIMM.

- UPMEM PIM: Architecture and Programming.

- Coffee break (10:00am-10:20am)

- 10:20am-11:00am, Dr. Dimin Niu, “A 3D Logic-to-DRAM Hybrid Bonding Process-Near-Memory Chip for Recommendation System”.

- 11:00am-11:40pm, Dr. Christina Giannoula, “SparseP: Towards Efficient Sparse Matrix Vector Multiplication on Real Processing-In-Memory Architectures”.

- 11:40pm-12:20pm, Dr. Juan Gómez Luna, “Processing-Using-Memory: Exploiting the Analog Operational Properties of Memory Components”.

- Lunch break (12:20pm-1:20pm)

- 1:20pm-2:00pm, Dr. Manuel Le Gallo, “Deep learning inference using computational phase-change memory”.

- 2:00pm-2:40pm, Dr. Juan Gómez Luna, “Adoption issues: How to enable PIM?”

- 2:40pm-3:20pm, Dr. Juan Gómez Luna, “Introduction/preparation for hands-on labs”.

- Coffee break (3:20pm-3:40pm)

- Hands-on Lab (3:40pm-5:40pm)

- Programming and understanding a real processing-in-memory architecture.

| Time | Speaker | Title | Materials |

|---|---|---|---|

| 8:00am-8:40am | Prof. Onur Mutlu | Memory-Centric Computing | (PDF) (PPT) |

| 8:40am-10:00am | Dr. Juan Gómez Luna | Processing-Near-Memory: Real PNM Architectures Programming General-purpose PIM | (PDF) (PPT) |

| 10:20am-11:00am | Dr. Dimin Niu | A 3D Logic-to-DRAM Hybrid Bonding Process-Near-Memory Chip for Recommendation System | |

| 11:00am-11:40am | Dr. Christina Giannoula | SparseP: Towards Efficient Sparse Matrix Vector Multiplication on Real Processing-In-Memory Architectures | (PDF) (PPT) |

| 1:30pm-2:10pm | Dr. Juan Gómez Luna | Processing-Using-Memory: Exploiting the Analog Operational Properties of Memory Components | (PDF) (PPT) |

| 2:10pm-2:50pm | Dr. Manuel Le Gallo | Deep Learning Inference Using Computational Phase-Change Memory | |

| 2:50pm-3:30pm | Dr. Juan Gómez Luna | PIM Adoption Issues: How to Enable PIM Adoption? | (PDF) (PPT) |

| 3:40pm-5:40pm | Dr. Juan Gómez Luna | Hands-on Lab: Programming and Understanding a Real Processing-in-Memory Architecture | (Handout) (PDF) (PPT) |

Learning Materials

Recommended Materials

- Gómez-Luna, J., and Mutlu, O., Data-Centric Architectures: Fundamentally Improving Performance and Energy (227-0085-37L), ETH Zürich, Fall 2022.

- Mutlu, O., Ghose, S., Gómez-Luna, J., and Ausavarungnirun, R. A Modern Primer on Processing in Memory. In Emerging Computing: From Devices to Systems, 2023.

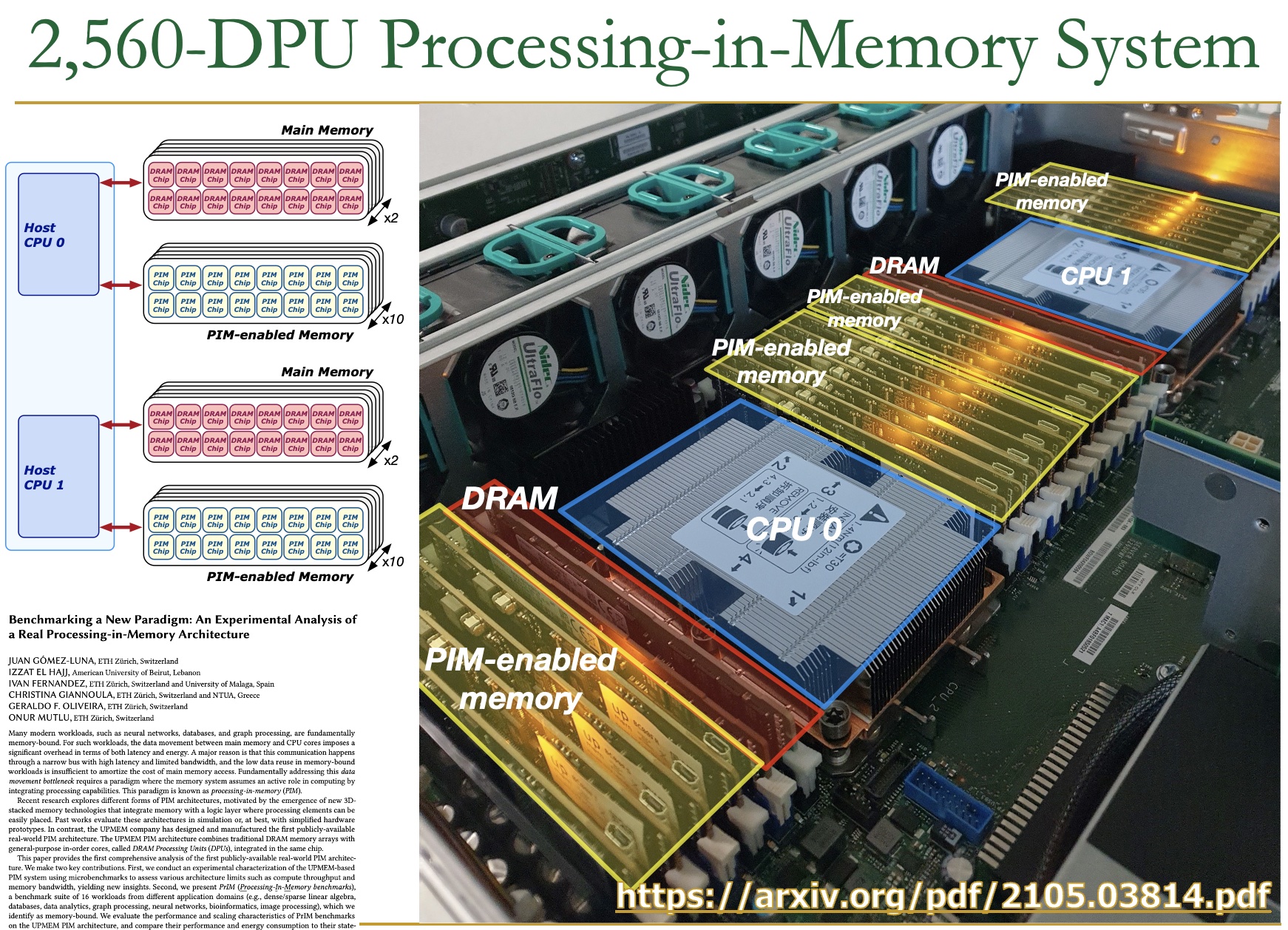

- Gómez-Luna, J., El Hajj, I., Fernandez, I., Giannoula, C., Oliveira, G. F., and Mutlu, O. (2022). Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System. IEEE Access, 2022.

- Giannoula, C., Fernandez, I., Gómez-Luna, J., Koziris, N., Goumas, G., and Mutlu, O. SparseP: Towards Efficient Sparse Matrix Vector Multiplication on Real Processing-In-Memory Architectures. SIGMETRICS 2022.

- Olgun, A., Gómez-Luna, J., Kanellopoulos, K., Salami, B., Hassan, H., Ergin, O., and Mutlu, O. PiDRAM: A Holistic End-to-end FPGA-based Framework for Processing-in-DRAM. ACM TACO, 2022.

More Learning Materials

- Mutlu O., Memory-Centric Computing (IMACAW Keynote Talk at DAC 2023), July 2023:

- Processing-in-memory: A workload-driven perspective (summary paper about recent research in PIM):

- Processing Data Where It Makes Sense: Enabling In-Memory Computation (summary paper about recent research in PIM):

- Processing-in-Memory course (Spring 2022):